Product Summary

The XC5202-PQ100AKM is a Field-Programmable Gate Array. The XC5202-PQ100AKM is engineered to deliver low cost. Building on experiences gained with three previous successful SRAM FPGA families, the device brings a robust feature set to programmable logic design. The VersaBlock. logic module, the VersaRing I/O interface, and a rich hierarchy of interconnect resources combine to enhance design flexibility and reduce time-to-market. Complete support for the XC5202-PQ100AKM is delivered through the familiar Xilinx software environment.

Parametrics

XC5202-PQ100AKM absolute maximum ratings: (1)Supply voltage relative to GND, VCC: -0.5 to +7.0 V; (2)Input voltage with respect to GND, VIN: -0.5 to VCC +0.5 V; (3)Voltage applied to 3-state output, VTS: -0.5 to VCC +0.5 V; (4)Storage temperature (ambient), TSTG: -65 to +150℃; (5)Maximum soldering temperature (10 s @ 1/16 in. = 1.5 mm), TSOL: +260℃; (6)Junction temperature in plastic packages, TJ: +125℃; (7)Junction temperature in ceramic packages, TJ: +150℃.

Features

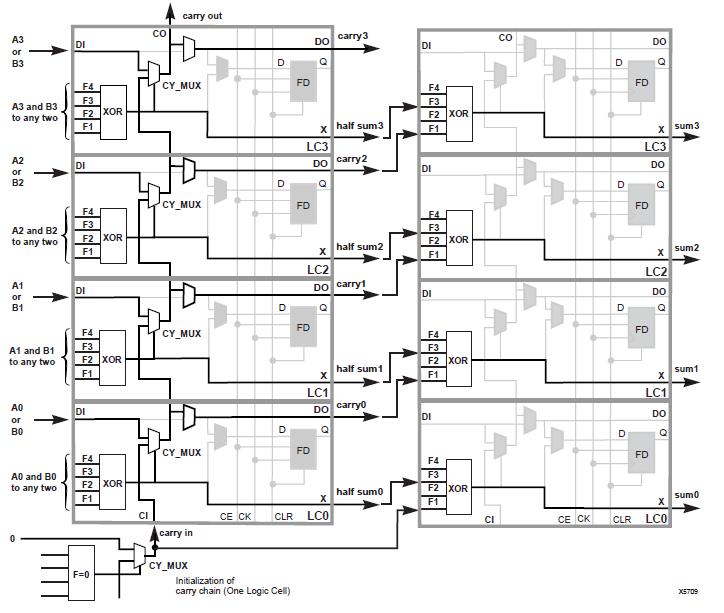

XC5202-PQ100AKM features: (1)System performance beyond 50 MHz; (2)6 levels of interconnect hierarchy; (3)VersaRing. I/O Interface for pin-locking; (4)Dedicated carry logic for high-speed arithmetic functions; (5)Cascade chain for wide input functions; (6)Built-in IEEE 1149.1 JTAG boundary scan test circuitry on all I/O pins; (7)Internal 3-state bussing capability; (8)Four dedicated low-skew clock or signal distribution nets.

Diagrams

|

XC5200 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC5200 Series |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC5202-5PQ100C |

|

IC - FPGA SPEED GRADE 5 COM TEMP |

Data Sheet |

Negotiable |

|

||||

|

XC5202-6PC84C |

|

IC FPGA 64 CLB'S 84-PLCC |

Data Sheet |

Negotiable |

|

||||

|

XC5202-6PQ100C |

|

IC FPGA 64 CLB'S 100-PQFP |

Data Sheet |

Negotiable |

|

||||

|

XC5204-5PC84C |

|

IC FPGA 120 CLB'S 84-PLCC |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))